This Blog contains VLSI Projects for engineering students

Best VLSI Projects for Engineering Students

Another well-organized VHDL project is the matrix multiplication design on FPGA Xilinx using Core Generator. If you want to learn how to use a Verilog module in VHDL design, this VHDL project provides a VHDL example code on instantiating a Verilog design on a bigger VHDL project.

Bluetooth Based Wireless Home Automation System

- Vlsi projects using verilog vlsi based projects for ece vlsi mini projects using verilog code fpga based projects using verilog vhdl mini projects simple verilog projects verilog projects with source code vhdl based projects with code verilog projects download verilog mini projects verilog project ideas vlsi mini projects using vhdl code vlsi.

- Aug 06, 2017 In this project, we present the design and implementation of the efficient hardware architecture for VGA monitor controllers based on Spartan3 FPGA Image Processing Kit.The design implements the bouncing ball in the VGA monitor using VHDL Code The ability to provide multiple display resolutions (up to WXGA 1280× 800) and a customizable internal FIFO make the proposed architecture.

Technology advancements have made possible the implementation of embedded systems within home appliances. This has added new capabilities and features, however, most of the time, the implementations are proprietary and networking is not always possible. Yet there is an increasing demand for smart homes, where appliances react automatically to changing environmental conditions and can be easily controlled through one common device. This paper presents a possible solution whereby the user controls devices by employing a central Field Programmable Gate Array (FPGA) controller to which the devices and sensors are interfaced. Control is communicated to the FPGA from a mobile phone through its Bluetooth interface. This results in a simple, cost-effective, and flexible system, making it a good candidate for future smart home solutions.

FPGA Based Robotic ARM Controller

A robotic arm is a type normally programmable mechanical arm, which can be used to pick and place various objects in the industries from one place to another place. It may be the sum total of the mechanism or may be part of a more complex robot. The parts of these manipulators or arms are interconnected through articulated joints that allow both a rotational movement. The FPGA based project is implemented using Spartan3an Project Kit and Robotic ARM kit.

Cloud based temperature Monitoring system using IOT

Building a cloud-based monitoring system is very important to reduce the cost of maintaining servers, to avoid data losses and to make the access easy with multiple internet-connected devices ( computer, tablet, mobile phone) at the same time anywhere in the world. There are various industrial areas it requires you to monitor temperature and update the status to the cloud. Food preservation is one of the areas where the temperature must be maintained at the lowest level. IOT based temperature monitoring system help us to monitor the food preservation system temperature and update the data to the cloud at the regular interval. This IOT system can be constructed using Spartan3an FPGA Starter Kit, Wi-Fi Module, and IOT Cloud server.

Multi Channel UART using FPGA

To meet modern complex control systems communication demands, the project presents a multi-channel UART controller based on FIFO(First In First Out) technique and FPGA(Field Programmable Gate Array). The project presents the design method of asynchronous FIFO and structure of the controller implemented in Spartan3an FPGA Project kit. This controller is designed with FIFO circuit block and UART (Universal Asynchronous Receiver Transmitter) circuit block within FPGA to implement communication in modern complex control systems quickly and effectively. From the communication sequence diagrams, it is easy to know that this controller can be used to implement communication when master equipment and slaver equipment are set at different Baud Rate. It also can be used to reduce synchronization error between sub-systems in a system with several sub-systems. The controller is reconfigurable and scalable.

Linear and Morphological Image Filtering using FPGA Image Processing Kit

Field Programmable Gate Array (FPGA) technology has become a viable target for the implementation of real-time algorithms suited to image processing applications. The unique architecture of the FPGA has allowed the technology to be used in many applications encompassing all aspects of video image processing. Among those algorithms, linear filtering based on a 2D convolution, and non-linear 2D morphological filters, represent a basic set of image operations for a number of applications. In this work, an implementation of linear and morphological image filtering using a Spartan3 FPGA Image Processing Kit, for educational purposes, is presented. The system is connected to a serial port of a personal computer, which in that way form a powerful and low-cost design station.

FPGA Implementation of distance Measurement using Ultrasonic Sensor

The main objective of the project is to Find the distance of the obstacle in front of any automation system, a Spartan3 FPGA Image Processing Kit is used to measure trigger input and display the echo output result.

FPGA Implementation of Booth Multiplier using Spartan6 FPGA project Board

A new architecture, namely, Multiplier-and accumulator (MAC) based Radix-4 Booth Multiplication Algorithm for high-speed arithmetic logics have been proposed and implemented on Spartan6 FPGA project Board . By combining multiplication with accumulation and devising a hybrid type adder the performance was improved. The modified booth encoder will reduce the number of partial products generated by a factor of 2. Fast multipliers are essential parts of digital signal processing systems. The speed of multiply operation is of great importance in digital signal processing as well as in the general purpose processors. The number to be added is the multiplicand, the number of times that it is added is the multiplier, and the result is the product. Each step of addition generates a partial product.

Lifting based Discrete Wavelet Transform using Spartan3 FPGA Image Processing Kit

In this project, we implement algorithms for efficient implementation of lifting based Discrete Wavelet Transform (DWT) using Spartan3 FPGA Image Processing Kit. The basic principle behind the lifting based scheme is to decompose the finite impulse response (FIR) filters in the wavelet transform into a finite sequence of simple filtering steps. Lifting based DWT implementations have many advantages and have recently been proposed for the JPEG2000 standard for image compression. Consequently, this has become an area of active research and several architectures have been proposed in recent years. In this paper, we provide a survey of these architectures for both 1-dimensional and 2-dimensional DWT. The architectures are representative of many design styles and range from highly parallel architectures to DSP-based architectures to folded architectures. We provide a systematic derivation of these architectures along with an analysis of their hardware and timing complexities.

Tertix Game Implementation using Spartan3 FPGA Image Processing kit

This Project implements obstacle avoidance on the air when dish antenna is receiving the signal from the space station. The purpose of this project is to continuously receive satellite signals by sensing the interfering object and change the direction of reception. The project was implemented with the help of Spartan3an FPGA Starter Kit, Spartan3an interfacing card with stepper motor interface and Ultrasonic Sensor.

TIC TAC TOE game using Spartan3 FPGA Image Processing kit

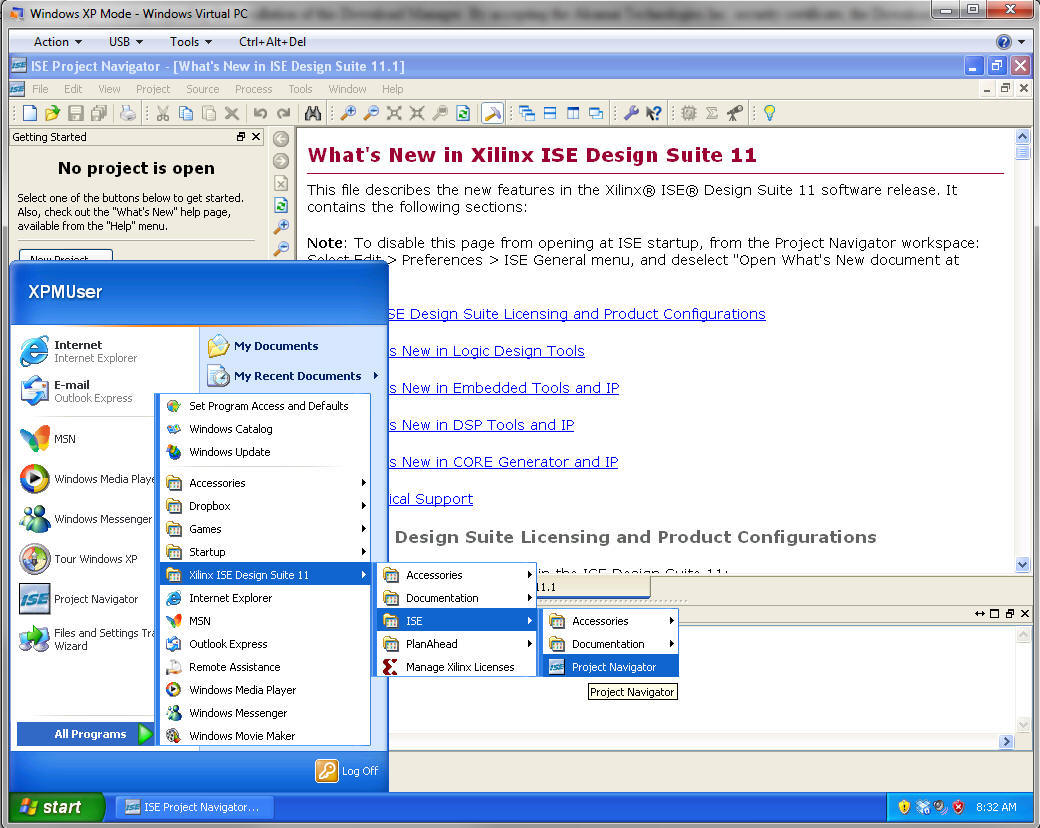

This design accomplished Tic-Tac-Toe game on Spartan3 FPGA Image Processing kit in VHDL. Firstly, designing the circuits and wiring on experiment board. Secondly, designing the algorithm and programming it in VHDL. Thirdly, synthesizing it in Xilinx Synthesis tool and then implementing it in Xilinx ISE developing suite. Finally, download it onto FPGA to run it. This design allows two players to play Tic-Tac-Toe game on the experiment board. The user plays the game from the keyboard. He uses the arrows to move a square on a 3×3 grid on the VGA display. The Xs and 0s are placed by pressing the space bar. The user can move a switch to choose the game mode. He can play against another player or alone against the design. When playing alone, after a X is placed the position of the 0 is returned but not yet shown on the display. Only after another key is pressed the 0 appears on the grid. When the game ends (X or 0 wins or draw game) the marks are automatically erased from the grid and the score is incremented on the seven-segment LED display.

Implementation of Medical Image Fusion using Spartan 3 FPGA

This Project implements FPGA Based Image fusion technique to analyze Medical images to diagnose various diseases. For medical diagnosis, Computed Tomography (CT) provides the best information on denser tissue with less distortion. Magnetic Resonance Image (MRI) provides better information on soft tissue with more distortion. With different types equipment output medical images in clinical applications, the idea of combining images from different equipment become very important.The experiments show that the method could extract useful information from combined images so that clear images are obtained. MATLAB is used to convert images into pixel-format files and to observe simulation results. To implement this paper XPS & VB are needed. In Xilinx Platform Studio, first select hardware & software components then by adding source and header files & converting into bit streams and download into Spartan3 FPGA Image Processing Kit, to obtain the fused image.

BPSK Implementation on Xilinx System Generator using Spartan3 FPGA Image Processing Kit

With the recent advent of hardware description languages (e.g., Verilog or VHDL) and digital implementation for field-programmable gate arrays (FPGAs), substantial academic digital design projects become practicable. In the present paper, the design of a digital binary-phase-shift-keying (BPSK) modulator and a detector is described. The project details the design of the components (e.g., multiplexer, FIR low pass filter and comparator) and the simulation of the entire system. The entire system was designed using the Matlab’s Simulink program and system generator block set and implemented on a Spartan3 FPGA Image Processing Kit. The steps taken to simulate the modulation blocks are shown.

VGA Based Bouncing Ball interface using Spartan3 FPGA Image Processing Kit

FPGA based Median Filter Implementation using Spartan3 FPGA Image Processing Kit

Vhdl Projects With Code Free Download For Windows 10

FPGA Based Sobal Edge Detection using Spartan3 FPGA Project Kit

FPGA Implementation of Keyboard Learner using Spartan3 FPGA Image processing kit

Generating PWM Signals With Variable Duty Cycle using FPGA

Field Programmable Gate Arrays (FPGA) provide very good hardware design flexibility. This paper specifies the generation of PWM signals for variable duty cycles using VHDL. Pulse Width Modulation found in large number of applications as a voltage controller. It is used in controlling output voltage of inverter in most of the applications.PWM has a fixed frequency and a variable voltage. Voltage value changes from 0V to 5 V. The advantage of this method is that it is used to generate High-frequency variable duty cycle PWM output. The VHDL code is written and synthesized using Xilinx ISE. Results are verified by downloading the code into SPARTAN 6 FPGA.

Implementation of Digital Clock using Spartan3an FPGA Evaluation Kit

Electronic clocks have predominately replaced the mechanical clocks. They are much reliable, accurate, maintenance free and portable. In general, there are two kinds of electronic clocks. They are analog clock and digital clock. But digital clocks are more common and independent of external source. It would be needed the controlled devices and implementation of software for microcontroller control system because the hardware devices cannot do any desired task to execute. In this paper, the Spartan3an FPGA based digital clock is constructed with XC3S50an and its software program is written with VHDL language. Various types of digital clocks and modules are available in the market nowadays but this clock is different at least in the accurate time. To be controlling in FPGA is only the feature of the clock. The input frequency is taken from the 50 Hz clock frequency circuit. To show the time, 2×16 LCD is used.

FPGA Implementation of PIR Based Security alert System using Spartan 3an FPGA Starter Kit

PIR motion detectors are perhaps the most frequently used for security device. Passive IR motion detectors are usually designed to provide an indication to an alarm panel in response to detecting IR that is indicative of motion of the object. The alarm panel is responsive to receipt of the breach indication to cause an alarm condition to occur. When a person or motor vehicle enters a monitored area, PIR motion detectors are commonly used in conjunction with indoor or outdoor to turn on a light in response to a person moving in the field of view monitored by the motion detector. Someone enters secured places, immediately it will send sms for the Corresponding people. The people can understood something happens in host section. At the Same time camera keep on capturing images at the host place and saved into the computer. When the owner in remote place, they got messages to the host section by sms, they log into the host section computer through GPRS and WAP enable mobile, they can view all information of the host section images by mobile phone.

FPGA Implementation of AES Algorithm using Spartan6 FPGA Project Kit

With the current ubiquity of computer networks, distributed systems in general, and the Internet in particular, cryptography has become an enabling technology to secure the information infrastructures we are building, using, and counting on in daily life. In present days, almost every relevant communication system requires secure data transfer in order to maintain the privacy of the transmitted message. Hardware implementation on FPGA offers a quicker and customizable solution. I use Very High Speed Integrated Circuit Hardware Decryption Language (VHDL) for synthesizing logic design. The existing project uses Spartan6 FPGA Project Kit which is an integrated circuit development platform based on the Xilinx Spartan 6 FPGA.

Vhdl Projects With Code free. download full

FPGA Based Wireless Temperature Monitoring system using Spartan3an Starter Kit

Vhdl Pdf

This project implements Temperature monitoring system for Agricultural field using Spartan3an FPGA Starter kit. The most important factors for the quality and productivity of plant growth are temperature and humidity. Continuous monitoring of these environmental variables gives information to the grower to better understand, how each factor affects growth and how to manage maximal crop productiveness .The optimal greenhouse climate adjustment can enable us to improve productivity and to achieve remarkable energy savings – especially during the winter in northern countries. The system itself was usually simple without opportunities to control locally heating, lights, ventilation or some other activity, which was affecting the greenhouse interior climate. For the implementation of agricultural technologies, low cost and real time remote monitoring are needed, in this sense, programmable Logic Devices (PLDs) present as a good option for the technology development and implementation.